Western Digital������RISC-V SweRV Coreԭʼ����Ϊ�ڲ��ܹ�����

2018-12-06 17:12

��ΪRISC-V��������ڳ�Ա�Ĺȸ轫չʾ��TensorFlow Lite��������������������RISC-VоƬ������Zephyr����ϵͳ��Ƕ��ʽϵͳ��

�ڳ���һ��ʱ�䣬������������Ҫ�����չ�Ľ��գ������ܵ���ϣ���ܹ������������ˣ�Ҳ��������ټܹ���Ȩ��֧��������Դ��RISC-V ��ҵ�������һ�������ƣ���Western Digital Ҳ��RISC-V ����������Դ����������Ҳ������WD �滮��RISC-V SweRV Core ԭʼ����У�һ������ΪWestern Digital �ڲ��ܹ�������ͬʱҲ��Ϊ֧���������չ��RISC- V �ܹ���̬�������ס�

RISC-V SweRV Core ����WD ���滮��32 λԪRISC-V �ܹ�������˫����/ superscalar ��ƣ��߱�9 ���ߣ���ͬʱ���벢ִ�ж��ָ�������̳�ʽִ��ʱ�䣬��Ϊ����ѭ��ִ�еĺ�����ƣ�����28nm �´ﵽ1.8GHz ��ʱ�������߱�4.9 CoreMarks/Mhz ���ܣ� Western Digital �ƻ�������ܹ���Ϊ��̬Ӳ������������������֮�ã���ϣ�����ɿ�Դ�ṩ��������Ӧ�ÿ������롣

ͬʱWestern Digital Ҳ������ΪOmniXtend �������п�Դ������һ��������·�ṹʵ�ֿ�ȡ�����Դ���ļ��������ɼ����嵼���ϵͳ�ܹ����ɹᴮ���������������ѧϰ�������� GPU �� FPGA �Ƚ������ϵĴ�ȡ�����������֧Ԯδ�����㡢���桢��������I/O Ԫ�����ӵĽ�������ΪĿ�ꡣ

��������RISC-V �Ŀ����ṩ��Դ��SweRV ָ�ģ����������ģ�������ṩ�����龳����RISC-V ִ�е��ȶ��ԣ������жϺͻ����Ŵ�������ģ����Ҳ��Western Digital ����ִ�г���100�ڸ�ָ�����ϸ�ģ������֤SweRV Core ��ƽ̨��ϣ�����ɽ��˿�Դ��RISC-V �������ܹ���֤������������ơ�

�������

王健林许家印游艇曝光 网友:这次真是贫穷限制了我们的想像力

王健林许家印游艇曝光 网友:这次真是贫穷限制了我们的想像力2018-04-16 16:32

三季度全球可穿戴设备出货量上涨94.6%,苹果稳…

三季度全球可穿戴设备出货量上涨94.6%,苹果稳…2019-12-10 17:52

Samsung新专利曝光全面屏没有刘海

Samsung新专利曝光全面屏没有刘海2018-05-13 13:33

全幅高速连拍Canon1DX单机售28800元

全幅高速连拍Canon1DX单机售28800元2018-04-09 17:32

华为Mate X预计供货20万台左右

华为Mate X预计供货20万台左右2019-06-30 15:50

轻量级入门机:FujifilmX-M1无反登场

轻量级入门机:FujifilmX-M1无反登场2018-01-03 12:00

闪光灯竟有这么多花样魅蓝E2评测

闪光灯竟有这么多花样魅蓝E2评测2018-05-29 19:33

中科循环经济研究院在沧州成立

中科循环经济研究院在沧州成立2020-12-28 16:52

2018春节第一新机 魅蓝E3背面设计捉眼

2018春节第一新机 魅蓝E3背面设计捉眼2019-02-19 05:37

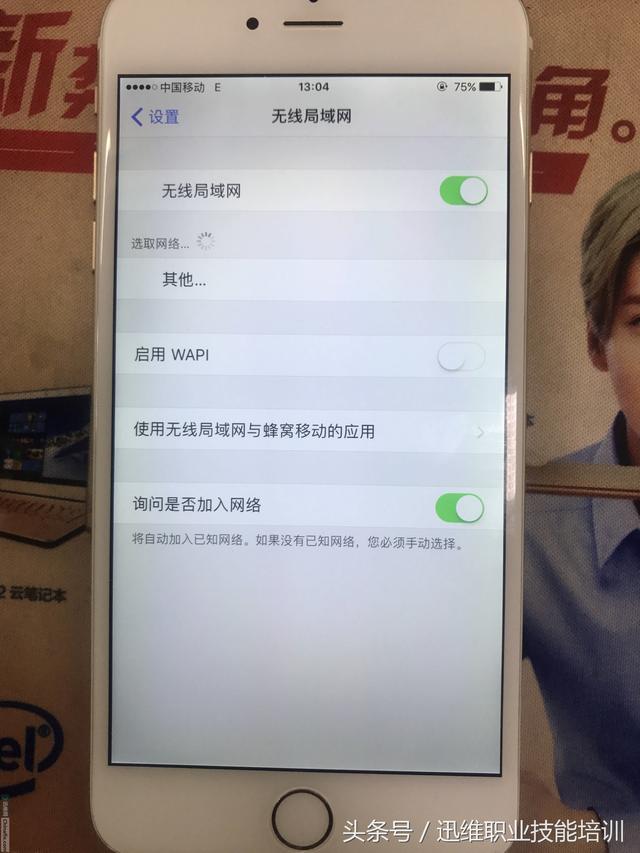

iPhone6Plus搜不到WiFi 手机店没修好 大神思路清晰一招搞定

iPhone6Plus搜不到WiFi 手机店没修好 大神思路清晰一招搞定2018-05-02 14:31

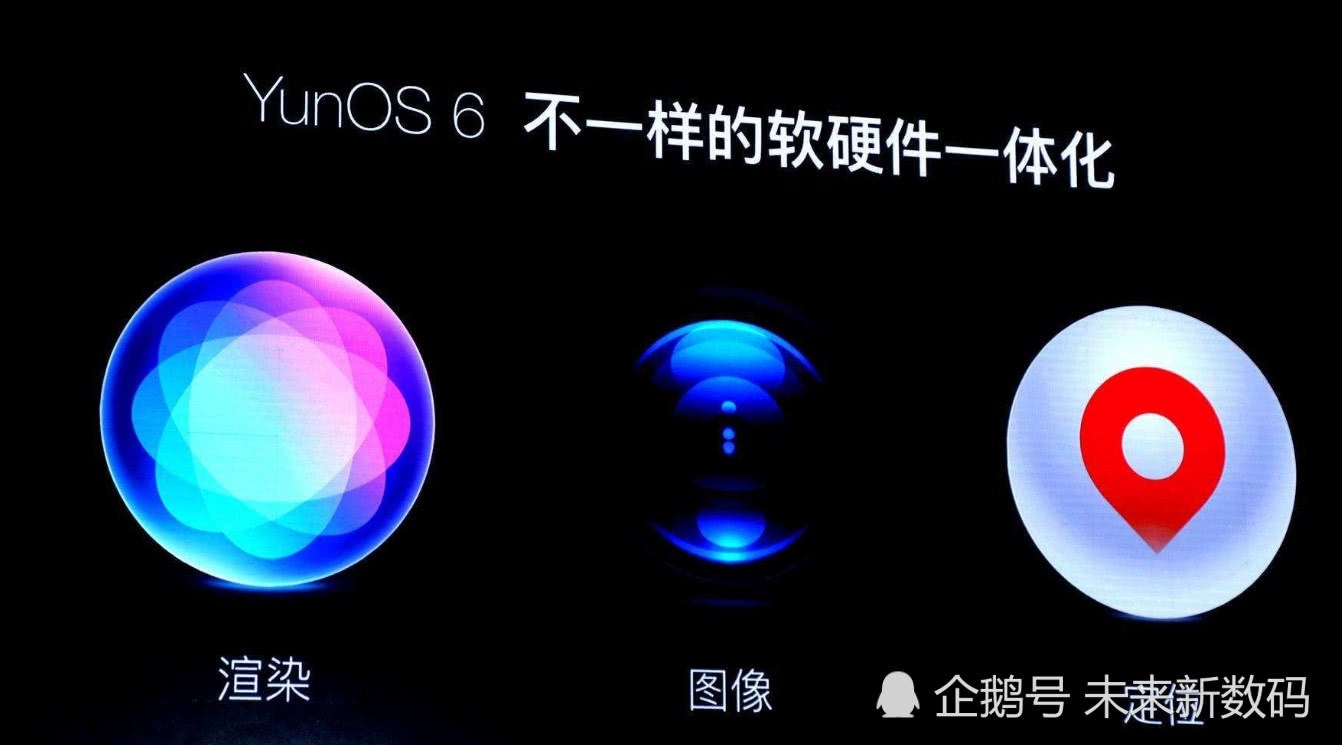

阿里YunOS即将到来 目前已有国产手机支持 期待吗?

阿里YunOS即将到来 目前已有国产手机支持 期待吗?2018-04-29 20:31

霸屏了!问卷网八周年感恩回馈活动火热进行中!

霸屏了!问卷网八周年感恩回馈活动火热进行中!2021-07-22 19:46

360摄像机3C云台电池版开启预售 创新“不插电…

360摄像机3C云台电池版开启预售 创新“不插电…2021-03-20 09:54

外媒报道:LG正研发新款翻盖式可折叠手机

外媒报道:LG正研发新款翻盖式可折叠手机2018-07-06 05:31

- 扎克伯格夫妇约会给孩子言传身教 扎克伯格家首次曝光

2019-12-05 18:53

5799元起 三星GalaxyS9/S9+勃艮第红版发布 三大女神代言

5799元起 三星GalaxyS9/S9+勃艮第红版发布 三大女神代言2018-05-08 17:32

印度造iPhone终于上市 但果粉依旧很失望

印度造iPhone终于上市 但果粉依旧很失望2018-09-22 00:32

更生行薪酬ETC:智能薪酬市场的领跑者

更生行薪酬ETC:智能薪酬市场的领跑者2019-08-20 11:55

魔兽争霸:守城关卡的设定十分经典 那么战役中最经典的是哪关?_希尔瓦娜斯

魔兽争霸:守城关卡的设定十分经典 那么战役中最经典的是哪关?_希尔瓦娜斯2019-06-30 14:46

脑洞飘出天际的科研队伍开发出3D打印水质检测器

脑洞飘出天际的科研队伍开发出3D打印水质检测器2018-08-05 18:31