MIT

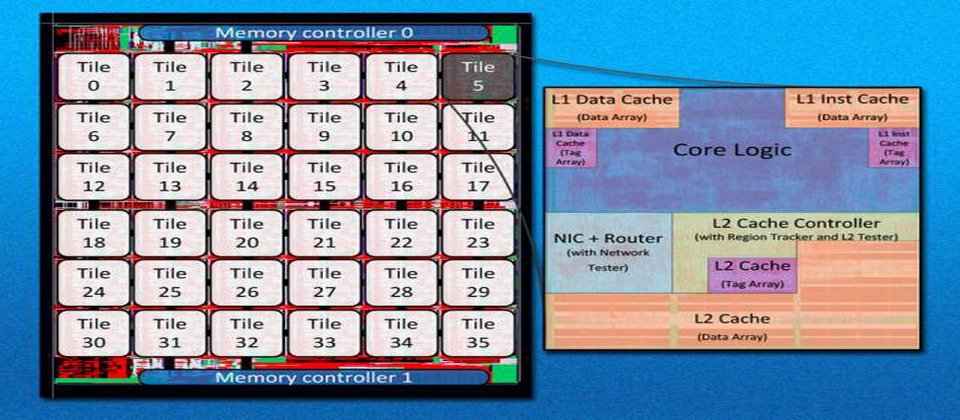

新一代处理器核心数越来越多,但核心间的资料交换复杂度也越高,成为了超多核心处理器提升效能的瓶颈。近日,在国际计算机架构大会(International Symposium on Computer Architecture,ISCA)上,麻省理工研究人员则公开最新开发的36核心处理器优化技术和实作成品,在处理器内部增加了资料路由排序机制,解决核心数越来越多后,衍生的快取一致性和执行效能问题。

(完整论文全文)

一般处理器核心与核心之间,主要是透过单一资料总线(bus)来进行沟通,好处在于透过snoopy协定,可让核心与核心在沟通时保持快取资料一致性,坏处是当两个核心沟通时就会占用资料总线,导致其他核心必须延迟等待,而随着核心数量越多时,等待问题也就越明显,往往也就容易造成多核处理器执行效能不彰。

不过麻省理工研究团队则是找到新方法来改善这个问题,该校电气工程和计算机科学教授Li-Shiuan Peh表示,尽管目前已有不少针对多核心处理器的芯片网络机制(network-on-chip)进行的研究,不过该研究小组则是在此芯片网络机制下加入一个具“迷你路由”功能的影子网络(shadow network),以解决多核心快取一致性和延迟等待问题。

根据研究小组成员Bhavya Daya指出,在这个芯片网络机制下,每颗核心都能迅速与它相邻核心进行沟通,而不同的核心之间则可透过影子网络(shadow network)方式沟通,每当核心接收到相关联的核心对主网络发出请求时,就会经由影子网络的节点找到最佳资料传递路径让其迅速通过,以减少其他核心执行时的等待周期时间。

而核心内的迷你路由功能,也能纪录下每颗核心到达另一颗核心的时间间隔,让核心之间的资料传送变得更加有序,经由这种资料传递方式也能解决过往多核心与快取一致性问题,而随着核心数量越多,也代表可供连结路径也变更多,也能提升核心之间的使用率。

此外,在处理器芯片内的影子网络也具备有分层优先权机制,以36核心来说,在一间隔时间,核心1与核心10同时皆发出请求时,核心1拥有较高的优先权,此时,尽管处理器的路由可能先收到核心10发出请求,但仍然会等核心1的资料封包通过后才会执行核心10的请求,不过每隔一段时间芯片内的核心优先等级就会被重新洗牌标注不同优先权,确保能作为长久使用。

另外,根据研究人员的测试结果也发现,在进行模拟36核心以及64核心测试环境时,采用此芯片网络技术的处理器比起没采用的处理器,在效能分别提升了将近24.1%与12.9%。

不过Bhavya Daya也指出,目前这种高效能36核心处理器还在原型测试阶段,接下来该研究小组将会进行调整,并改套用在Linux系统中测试其效能表现。未来,MIT也有意计划以Verilog的硬件描述语言方式,将此芯片技术的开放源代码分享出来,让更多人共同参与开发。

2014/6/25更正说明:原文提及MIT新发表的36核心处理器,颠覆传统处理器架构,且是多核心处理器技术的大变革叙述有误,正确应为MIT提供一个新的芯片网络(Network-On-Chip)架构方法,可在多核心之间建构一个具 “网络优先级”的路由功能网络,用以解决多核心间的快取一致性,进而提高多核心的使用率来优化处理器效能。(内文已更正)

另外原提及核心与核心之间的“沟通”,但并未说明其沟通方式,完整为在核心之间透过单一总线来沟通,符合Snoopy协定快取一致性,而当核心数越多时,核心间快取一致性就会发生问题,造成处理器执行上的等待延迟越长。(内文已补充)

相关文章

YouTube更新违反规定政策,提升惩处透明度和一致性

YouTube更新违反规定政策,提升惩处透明度和一致性2023-12-31 14:00:52

传苹果将把中国iCloud正式交给本地化经营 苹果手机icloud换区存储操作

传苹果将把中国iCloud正式交给本地化经营 苹果手机icloud换区存储操作2023-12-27 18:34:43

刘德华代言什么手机?刘德华成华为Mate 60 RS非凡大师华为5G新手机代言人

刘德华代言什么手机?刘德华成华为Mate 60 RS非凡大师华为5G新手机代言人2023-09-26 21:55:08

WebOS新系统:Palm Pre手机最新款高价登港

WebOS新系统:Palm Pre手机最新款高价登港2023-06-23 15:39:14

帮助企业组织对抗勒索软件,资安通报机构设立防护专区,可协助事前、事中与事后因应

帮助企业组织对抗勒索软件,资安通报机构设立防护专区,可协助事前、事中与事后因应2023-06-22 09:36:10

蔚来全系产品降价3万 取消免费换电 换一次电池180元

蔚来全系产品降价3万 取消免费换电 换一次电池180元2023-06-12 17:27:49

电商平台三巨头开打最大规模折扣 价格战再次打响

电商平台三巨头开打最大规模折扣 价格战再次打响2023-03-05 18:58:40

爱立信节省成本裁员四千人 爱立信全球员工总数五分之一

爱立信节省成本裁员四千人 爱立信全球员工总数五分之一2023-02-24 22:27:29

蜜芽关停近况,八位数重金买三字顶级新域名mia.com也关闭

蜜芽关停近况,八位数重金买三字顶级新域名mia.com也关闭2023-02-23 16:18:14

联想CEO杨元庆:联想集团需要裁员32%削减部分业务支出

联想CEO杨元庆:联想集团需要裁员32%削减部分业务支出2023-02-18 12:45:25

蓝色光标2022营收亏损18亿 客户预算减少明显

蓝色光标2022营收亏损18亿 客户预算减少明显2023-02-18 12:40:08

三星工厂或将80%生产转至越南 因本地劳动力成本上升

三星工厂或将80%生产转至越南 因本地劳动力成本上升2023-02-17 23:09:16

香港八达通卡如何激活?没用失效过期余额怎么办

香港八达通卡如何激活?没用失效过期余额怎么办2023-02-17 18:34:51

中兴通讯被曝将裁员20% 称只裁国外的

中兴通讯被曝将裁员20% 称只裁国外的2023-02-17 18:33:26

苹果新iPhone15Pro手机终于改用USB-C(火牛)数据线??Lightning充电接口退出

苹果新iPhone15Pro手机终于改用USB-C(火牛)数据线??Lightning充电接口退出2023-02-17 16:57:22

突发!蓝色光标曾为中国民企500强龙头 如今业绩亏损断崖下跌

突发!蓝色光标曾为中国民企500强龙头 如今业绩亏损断崖下跌2023-02-16 14:31:19

三星发布自家carplay车载中控系统 Car Mode for Galaxy 可以连接carplay吗?

三星发布自家carplay车载中控系统 Car Mode for Galaxy 可以连接carplay吗?2023-02-14 00:53:17

Opera浏览器宣布集成ChatGPT 一键生成网页内容摘要

Opera浏览器宣布集成ChatGPT 一键生成网页内容摘要2023-02-14 00:32:08

谷歌google计划重返进入中国市场?但结果可能令你失望

谷歌google计划重返进入中国市场?但结果可能令你失望2023-02-13 16:57:15

Zoom紧急裁员1300人 佔员工总数15%

Zoom紧急裁员1300人 佔员工总数15%2023-02-08 14:59:11

最新资讯

YouTube更新违反规定政策,提升惩处透明度和一致性2023-12-31 14:00:52

YouTube更新违反规定政策,提升惩处透明度和一致性2023-12-31 14:00:52 美国法院裁定阿里须为Squishmallows玩具侵权案答辩2023-12-28 19:59:34

美国法院裁定阿里须为Squishmallows玩具侵权案答辩2023-12-28 19:59:34 小米汽车传员工3700人 雷军称小米汽车不可能卖9万92023-12-28 19:41:57

小米汽车传员工3700人 雷军称小米汽车不可能卖9万92023-12-28 19:41:57 吉利飙逾6% 电动车品牌极氪新车款极氪007昨上市 预售价格22.99万元2023-12-28 19:30:28

吉利飙逾6% 电动车品牌极氪新车款极氪007昨上市 预售价格22.99万元2023-12-28 19:30:28 日本丰田汽车厂11月全球产量创新高2023-12-28 19:26:02

日本丰田汽车厂11月全球产量创新高2023-12-28 19:26:02

手机

中国11月手机出货量增34% 5G手机出货量2709.2万部2023-12-28 19:27:57

中国11月手机出货量增34% 5G手机出货量2709.2万部2023-12-28 19:27:57 荣耀发布新一代旗舰荣耀Magic5系列,新款上市价格分期0首付3999元起2023-03-06 16:12:32

荣耀发布新一代旗舰荣耀Magic5系列,新款上市价格分期0首付3999元起2023-03-06 16:12:32 美国商务部指违禁,长江存储被美国拜登制裁名单面临停工裁员2023-02-17 18:41:53

美国商务部指违禁,长江存储被美国拜登制裁名单面临停工裁员2023-02-17 18:41:53 苹果Apple iOS车载系统CarPlay支持哪些更多汽车品牌2023-02-02 17:33:27

苹果Apple iOS车载系统CarPlay支持哪些更多汽车品牌2023-02-02 17:33:27 香港去哪买三星手机回来吗? 买香港便宜售价手机市场地点和网站2023-02-02 11:03:11

香港去哪买三星手机回来吗? 买香港便宜售价手机市场地点和网站2023-02-02 11:03:11

数码

华为5G芯片正式亮相:预示华为将发首款5G手机2023-08-31 13:22:33

华为5G芯片正式亮相:预示华为将发首款5G手机2023-08-31 13:22:33 腾讯传计划放弃虚拟现实VR硬件计划2023-02-17 23:32:30

腾讯传计划放弃虚拟现实VR硬件计划2023-02-17 23:32:30 三星手机份额大跌!三星手机中国市场份额变化国内仅剩3%2023-02-01 17:06:15

三星手机份额大跌!三星手机中国市场份额变化国内仅剩3%2023-02-01 17:06:15 三星手机份额大跌在中国没市场了!国内市场占有率仅剩1%国外比苹果销量高2023-02-01 16:59:53

三星手机份额大跌在中国没市场了!国内市场占有率仅剩1%国外比苹果销量高2023-02-01 16:59:53 vivo发布2022 vivoNEX手机极简易浏览器下载:简洁流畅无广告!2022-12-02 17:29:30

vivo发布2022 vivoNEX手机极简易浏览器下载:简洁流畅无广告!2022-12-02 17:29:30

科技

中兴受美国制裁事件 被罚了20亿美元过程事件始末 中兴被制裁后公司现状2023-11-02 22:12:46

中兴受美国制裁事件 被罚了20亿美元过程事件始末 中兴被制裁后公司现状2023-11-02 22:12:46 B站怎么炸崩了哔哩哔哩服务器今日怎么又炸挂了?技术团队公开早先原因2023-03-06 19:05:55

B站怎么炸崩了哔哩哔哩服务器今日怎么又炸挂了?技术团队公开早先原因2023-03-06 19:05:55 苹果iPhoneXS/XR手机电池容量续航最强?答案揭晓2023-02-19 15:09:54

苹果iPhoneXS/XR手机电池容量续航最强?答案揭晓2023-02-19 15:09:54 华为荣耀两款机型起内讧:荣耀Play官方价格同价同配该如何选?2023-02-17 23:21:27

华为荣耀两款机型起内讧:荣耀Play官方价格同价同配该如何选?2023-02-17 23:21:27 google谷歌原生系统Pixel3 XL/4/5/6 pro手机价格:刘海屏设计顶配版曾卖6900元2023-02-17 18:58:09

google谷歌原生系统Pixel3 XL/4/5/6 pro手机价格:刘海屏设计顶配版曾卖6900元2023-02-17 18:58:09