三星计划在2021年推出3nm全栅晶体管

消息来源:baojiabao.com 作者: 发布时间:2024-05-04

三星电子计划于2021年推出FinFETS晶体管架构的后继产品,采用3纳米工艺节点的全栅晶体管(gate-all-around ,GAA)。这家韩国巨头还在本周二(5月22日)年度代工技术论坛上重申,今年下半年将开始使用极紫外(EUV)光刻技术开始7nm生产。

自二十一世纪初以来,三星和其他公司一直在开发GAA技术。 GAA晶体管是场效应晶体管(FET),在通道的所有四个侧面都有一个栅极,用于克服FinFET的物理缩放比例和性能限制,包括电源电压。

三星公司市场副总裁Ryan Sanghyun Lee表示,自2002年以来,三星专有的GAA技术被称为多通道FET(MBCFET)。据该公司介绍,MCBFET使用纳米片器件来增强栅极控制,显著提高晶体管的性能。

三星去年表示,它计划在2020年开始使用4纳米节点的GAA晶体管。然而,业界观察家预计GAA将在2022年之前投产。

Gartner的代工厂研究副总裁Samuel Wang表示,他预计三星将在2022年的某个时间点正式量产GAA晶体管。“看起来他们的行动速度比这还快,”Wang说。 图:Kevin Krewell

Kevin Krewell 说:“三星的路线图很激进,我已经知道他们在EUV上进展迅猛,但这也设置了一个很高的门槛。”

但是,Krewell补充说:“这仍然是一个出路,时间表可能会有变动。”

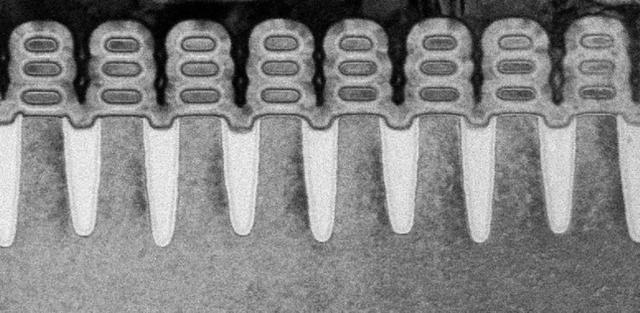

由IBM和合作伙伴三星、Globalfoundries建立的采用全栅技术的5nm晶体管的SEM图像。来源:IBM

去年6月,IBM和其研究联盟合作伙伴三星和Globalfoundries在日本京都举办的2017年超大规模集成电路技术和电路会议专题讨论会(2017 Symposia on VLSI Technology and Circuits conference)上,描述了他们为基于堆叠纳米片制造5纳米GAA晶体管而开发的工艺。据了解,包括英特尔和台积电在内的其他芯片制造商正在开发自己的下一代晶体管,其版本与FinFET类似,属于GAA FET。

三星重申计划在今年下半年开始使用EUV光刻技术进行大规模生产,采用7nm Low Power Plus工艺。三星预计将成为第一家将业界多年来寄予厚望的EUV设备投入商业化生产的芯片制造商。台积电和Globalfoundries宣布计划于2019年开始使用EUV进行商业化生产。

虽然光刻工具供应商ASML和先进芯片制造商们已经证明能够克服多年来困扰EUV发展的电源问题,但在商业生产中部署EUV所需的支持技术仍在开发和调整之中。

三星晶圆代工业务首席工程师Yongjoo Jeon周二表示,三星将使用内部开发的EUV掩模检测工具。对于三星来说,这是一个重要的优势,因为还没有类似的商业工具被开发出来,Jeon补充道。

Jeon表示,三星在没有保护EUV光罩免受颗粒污染掩膜情况下将率先部署EUV,这是另一项仍在开发中的技术。 Jeon说三星在EUV薄膜开发方面正取得进展,并且他相信最终能将该技术部署在自家EUV的生产过程中。

三星还在开发EUV光刻胶,并有望在今年晚些时候达到大规模量产要求的目标良率,Jeon说。

三星的工艺技术路线图还包括2019年的5nm FinFET和2020年的4nm FinFET生产工艺。

翻译:Mike Zhang

责编:Luffy Liu

本文授权编译自EE Times,版权所有,谢绝转载

相关文章

中兴受美国制裁事件 被罚了20亿美元过程事件始末 中兴被制裁后公司现状

中兴受美国制裁事件 被罚了20亿美元过程事件始末 中兴被制裁后公司现状2023-11-02 22:12:46

B站怎么炸崩了哔哩哔哩服务器今日怎么又炸挂了?技术团队公开早先原因

B站怎么炸崩了哔哩哔哩服务器今日怎么又炸挂了?技术团队公开早先原因2023-03-06 19:05:55

苹果iPhoneXS/XR手机电池容量续航最强?答案揭晓

苹果iPhoneXS/XR手机电池容量续航最强?答案揭晓2023-02-19 15:09:54

华为荣耀两款机型起内讧:荣耀Play官方价格同价同配该如何选?

华为荣耀两款机型起内讧:荣耀Play官方价格同价同配该如何选?2023-02-17 23:21:27

google谷歌原生系统Pixel3 XL/4/5/6 pro手机价格:刘海屏设计顶配版曾卖6900元

google谷歌原生系统Pixel3 XL/4/5/6 pro手机价格:刘海屏设计顶配版曾卖6900元2023-02-17 18:58:09

科大讯飞同传同声翻译软件造假 浮夸不能只罚酒三杯

科大讯飞同传同声翻译软件造假 浮夸不能只罚酒三杯2023-02-17 18:46:15

华为mate20pro系列手机首发上市日期价格,屏幕和电池参数配置对比

华为mate20pro系列手机首发上市日期价格,屏幕和电池参数配置对比2023-02-17 18:42:49

小米MAX4手机上市日期首发价格 骁龙720打造大屏标准

小米MAX4手机上市日期首发价格 骁龙720打造大屏标准2023-02-17 18:37:22

武汉弘芯遣散!结局是总投资1280亿项目烂尾 光刻机抵押换钱

武汉弘芯遣散!结局是总投资1280亿项目烂尾 光刻机抵押换钱2023-02-16 15:53:18

谷歌GoogleDrive网云盘下载改名“GoogleOne” 容量提升价格优惠

谷歌GoogleDrive网云盘下载改名“GoogleOne” 容量提升价格优惠2023-02-16 13:34:45

巴斯夫将裁员6000人 众化工巨头裁员潮再度引发关注

巴斯夫将裁员6000人 众化工巨头裁员潮再度引发关注2023-02-13 16:49:06

人手不足 韵达快递客服回应大量包裹派送异常没有收到

人手不足 韵达快递客服回应大量包裹派送异常没有收到2023-02-07 15:25:20

资本微念与李子柒销声匿迹谁赢? 微念公司退出子柒文化股东

资本微念与李子柒销声匿迹谁赢? 微念公司退出子柒文化股东2023-02-02 09:24:38

三星GalaxyS8 S9 S10系统恢复出厂设置一直卡在正在检查更新怎么办

三星GalaxyS8 S9 S10系统恢复出厂设置一直卡在正在检查更新怎么办2023-01-24 10:10:02

华为Mate50 RS保时捷最新款顶级手机2022多少钱?1.2万元售价外观图片吊打iPhone14

华为Mate50 RS保时捷最新款顶级手机2022多少钱?1.2万元售价外观图片吊打iPhone142023-01-06 20:27:09

芯片常见的CPU芯片封装方式 QFP和QFN封装的区别?

芯片常见的CPU芯片封装方式 QFP和QFN封装的区别?2022-12-02 17:25:17

华为暂缓招聘停止社招了吗?官方回应来了

华为暂缓招聘停止社招了吗?官方回应来了2022-11-19 11:53:50

热血江湖手游:长枪铁甲 刚猛热血 正派枪客全攻略技能介绍大全

热血江湖手游:长枪铁甲 刚猛热血 正派枪客全攻略技能介绍大全2022-11-16 16:59:09

东京把玩了尼康微单相机Z7 尼康Z7现在卖多少钱?

东京把玩了尼康微单相机Z7 尼康Z7现在卖多少钱?2022-10-22 15:21:55

苹果iPhone手机灵动岛大热:安卓灵动岛App应用下载安装量超100万次

苹果iPhone手机灵动岛大热:安卓灵动岛App应用下载安装量超100万次2022-10-03 22:13:45