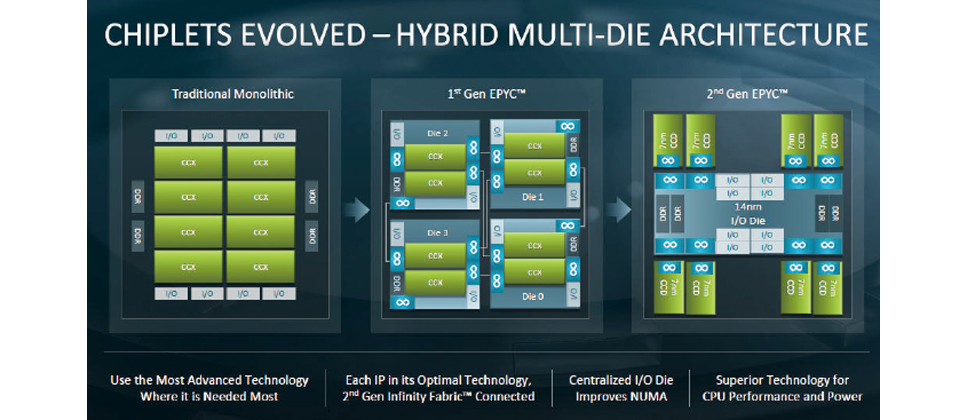

最近2年,越来越多新一代超多核心CPU设计也都开始整合MCM多芯片模组封装技术(Multi-Chip-Module),如AMD在设计新款64核心处理器时,就是采用这个技术,将原本一个更大核心,分拆成多个小核心,封装在多个晶粒里,再整合成单一CPU, 甚至还整合8个晶粒与一个共用I/O 晶粒的混合多芯片架构,借此来换取更多核心的增长空间。(图片来源/AMD)

在一颗服务器处理器中,放进完整功能的64个核心,为何处理器龙头英特尔还没实现,3年前才重返服务器市场的AMD却能够做到,甚至价格只要竞争对手Xeon处理器的一半,而且还更省电?关键就是AMD新款CPU采取老设计和新制程,前者是早在10年前就出现的MCM多芯片模组封装技术(Multi-Chip-Module),后者则是最先进的7奈米制程来提高核心密度,两者结合才能做得到。

服务器CPU核心的演进,从最早的单核、双核、四核到3年前多核的20核心以上,大约历经10多年发展,但是随着CPU核心数,从个位数突破到双位数,现在,想要在一颗CPU加入更多核心,比以前难度更高,除了处理器设计架构变得越来越复杂,需要投入制作成本也更高,例如,英特尔过去花了3年时间,才将最高阶Xeon处理器的核心,从24核提升到最高28核心,也才只多增加了4个运算核心。

两年内翻新CPU架构,抢先超前英特尔推出64核心CPU设计

但是从32核心翻倍提高到64核心,AMD仅花了两年时间就达成,在今年8月率先推出第二代EPYC系列x86处理器,就能提供高达64个运算核心,甚至接下来还有两款全新EPYC处理器,将在明、后两年问世,还能够替下一代CPU增加更多核心。

之所以能够在单颗CPU放进64核的一大关键,在于AMD采用了和以往截然不同的MCM多芯片封装技术,来设计新一代多核处理器,可以一次将多核心、多个晶粒(Die),封装在一个整合的单一CPU,来取代原本多核心单晶粒(Monolithic Die)的封装方式,借此来提高CPU总核心。

旧有MCM多芯片封装技术,成了新一代CPU加大核心的关键技术

不光是增加核心数,因为这颗超多核心处理器,是以整合多个单晶粒封装的方式,来取代以往将全部核心集中压缩在单一晶粒的旧有单芯片封装作法,因此,对于处理器厂商来说,设计出来的多核CPU,不仅功耗更低、良率也能提高不少。

有了MCM多芯片封装设计,处理器厂商在设计多核处理器时,就不一定非得要将所有核心都放进单一晶粒里,而是可以设计成多晶粒架构,将一个更大核心,分拆成多个小核心,封装在多个晶粒里,再整合成单一CPU。

而且比起原生多核设计,透过采用这个封装方式设计出来的多核CPU,不只可以容纳比原先更多的核心。甚至是可以达到突破性的成长,取得翻倍核心数。这正是AMD之所以可以很快提升处理器核心数量的关键。也是靠旧有原生多核心设计,难以实现达到的最大核心数,也只有透过采用MCM技术,才有办法做到。

但是MCM多芯片封装并不是新技术,早在1995年,英特尔推出Pentium Pro微处理器时,就曾采用MCM技术,来提高处理器执行效能,将L2内存与本体处理器电路同时封装到单一CPU芯片,更在相隔10年发表新款Pentium D与Xeon 5000系列同样利用此技术,推出首款双核心处理器。甚至更早之前,IBM也曾将MCM技术用于大型主机推出另一款双核处理器Power4。

不过,过去很长一段时间,主流多核心处理器,仍采原生多核设计, 直到近几年,采用这个设计来加大核心的原生多核设计CPU,在核心数量上很难有更高增长,才使得MCM多芯片封装技术重新崭露头角。

在2017年,AMD以这个技术搭配全新处理器架构,来打造出更大核心数的第一代服务器处理器EPYC,比英特尔Xeon多核处理器高出了8个核心,达到32核心之多。该处理器一推出,也在服务器市场引起热烈回响。

以往非主流的MCM多芯片封装技术,现在却成了新一代处理器加大核心的关键技术。

就连原本主张原生多核心设计的英特尔,也都不得不做出妥协,近来在设计新款多核心处理器时,也都开始采用MCM技术,以换取更高效能、更多核心的增长空间。例如,今年4月推出第2代Xeon Scalable系列处理器时,其中最高阶型号的Xeon Platinum 9200系列处理器,就提供了多达56核心,也就是采用这个技术来增加运算核心,以对抗AMD的64核心处理器。

为了冲刺更高核心,也挑战现有服务器CPU设计架构

不过,采用MCM多芯片封装作法,虽然可以很快提高核心,但是也带来一些新挑战,例如,各模组核心之间沟通,容易出现反应延迟,或效能减损等问题,也挑战现有服务器处理器的架构,也得跟上脚步,与时俱进。

所以,除了采用更先进MCM封装技术,AMD同时也持续改进处理器设计架构,甚至每更新一代,就翻新一次CPU架构,来对应最大核心数,以发挥出原有多核处理器预期的效益。

像是在推出第一代32核心EPYC处理器时,AMD总共设计了4个不同的小型晶粒,可以把多个核心放进单一晶粒,每个晶粒更是由两个CCX(CPU Complex)模组组成,单一个CCX内最多可放4个核心、L2快取和L3快取,总计8个CCX模组封装,整合成为一个32核心处理器,甚至每个晶粒上,都有独立I/O控制,也配置存取内存。

为了加快多核心之间的讯息沟通,AMD还开发出了一个全新Infinity Fabric高速互连架构,来提高各个CPU核心之间的沟通效率。

第二代64核EPYC处理器推出时,AMD再一次翻新CPU架构,采用更先进混合多芯片架构设计 (Hybrid Multi-Die Architecture),来打造全新的Zen2处理器架构,以放进比之前更多核心。

在这个混合多芯片架构设计下,每个晶粒体积比之前更小,因此,在单一CPU内可以封装更多晶粒,来达到增加更多核心的效果,例如,在64核CPU内整合8个晶粒与一个共用I/O 晶粒的混合多芯片架构。又因为单一模组的晶粒,能提供最多8核心 ,所以,AMD直接称作Chiplet(小芯片)。

通过在单一处理器内设计左右对称各4组合计8个小芯片(或晶粒),再通过中间高速互连网络设计的一个14奈米的I/O 晶粒互连,整合成单一64核CPU。

除了核心密度的提升,Zen2架构也有不少改进,例如,不仅重新设计执行工作流程(pipeline),还加倍提高浮点暂存器(Register),与加快单一暂存器指令的载入和储存等,来持续优化和增加新功能。

新的CPU架构在IPC (每时脉周期执行指令) 效能表现上,更较前代提高15%之多,另外,在执行AVX2指令集的浮点运算效能也有翻倍的提升。更进一步还加大处理器使用的L3快取,将内存总容量提高至256MB,来缩短CPU资料存取的反应时间。

AMD更宣称,透过采用混合多芯片架构,可以让这代CPU处理效能提高两倍,而且具备更强的平行运算处理能力,最大可以提供多达4倍的运算吞吐量(FLOPS)。

尤其,新的Zen2架构,采用最先进7奈米制程来生产64核CPU,从原本14奈米进一步缩小到7奈米,这也意谓著,在相同芯片面积下,可以封装更多晶体管来提高核心密度,例如,单是一颗采用7奈米64核CPU,其内含的晶体管就高达320亿个。

AMD采用8个7奈米小芯片模组设计,来组成64个运算核心丛集,再封装在单一CPU,也帮助处理器厂商在设计处理器时,不需要大幅增加功耗,就能提供更多核心,例如64核第二代EPYC处理器,最高TDP (热设计功耗)只比一代多出45瓦,达到225瓦,但核心数却足足多了一倍。这也是打造64核心处理器的另一大关键。

相关文章

YouTube更新违反规定政策,提升惩处透明度和一致性

YouTube更新违反规定政策,提升惩处透明度和一致性2023-12-31 14:00:52

传苹果将把中国iCloud正式交给本地化经营 苹果手机icloud换区存储操作

传苹果将把中国iCloud正式交给本地化经营 苹果手机icloud换区存储操作2023-12-27 18:34:43

刘德华代言什么手机?刘德华成华为Mate 60 RS非凡大师华为5G新手机代言人

刘德华代言什么手机?刘德华成华为Mate 60 RS非凡大师华为5G新手机代言人2023-09-26 21:55:08

WebOS新系统:Palm Pre手机最新款高价登港

WebOS新系统:Palm Pre手机最新款高价登港2023-06-23 15:39:14

帮助企业组织对抗勒索软件,资安通报机构设立防护专区,可协助事前、事中与事后因应

帮助企业组织对抗勒索软件,资安通报机构设立防护专区,可协助事前、事中与事后因应2023-06-22 09:36:10

蔚来全系产品降价3万 取消免费换电 换一次电池180元

蔚来全系产品降价3万 取消免费换电 换一次电池180元2023-06-12 17:27:49

电商平台三巨头开打最大规模折扣 价格战再次打响

电商平台三巨头开打最大规模折扣 价格战再次打响2023-03-05 18:58:40

爱立信节省成本裁员四千人 爱立信全球员工总数五分之一

爱立信节省成本裁员四千人 爱立信全球员工总数五分之一2023-02-24 22:27:29

蜜芽关停近况,八位数重金买三字顶级新域名mia.com也关闭

蜜芽关停近况,八位数重金买三字顶级新域名mia.com也关闭2023-02-23 16:18:14

联想CEO杨元庆:联想集团需要裁员32%削减部分业务支出

联想CEO杨元庆:联想集团需要裁员32%削减部分业务支出2023-02-18 12:45:25

蓝色光标2022营收亏损18亿 客户预算减少明显

蓝色光标2022营收亏损18亿 客户预算减少明显2023-02-18 12:40:08

三星工厂或将80%生产转至越南 因本地劳动力成本上升

三星工厂或将80%生产转至越南 因本地劳动力成本上升2023-02-17 23:09:16

香港八达通卡如何激活?没用失效过期余额怎么办

香港八达通卡如何激活?没用失效过期余额怎么办2023-02-17 18:34:51

中兴通讯被曝将裁员20% 称只裁国外的

中兴通讯被曝将裁员20% 称只裁国外的2023-02-17 18:33:26

苹果新iPhone15Pro手机终于改用USB-C(火牛)数据线??Lightning充电接口退出

苹果新iPhone15Pro手机终于改用USB-C(火牛)数据线??Lightning充电接口退出2023-02-17 16:57:22

突发!蓝色光标曾为中国民企500强龙头 如今业绩亏损断崖下跌

突发!蓝色光标曾为中国民企500强龙头 如今业绩亏损断崖下跌2023-02-16 14:31:19

三星发布自家carplay车载中控系统 Car Mode for Galaxy 可以连接carplay吗?

三星发布自家carplay车载中控系统 Car Mode for Galaxy 可以连接carplay吗?2023-02-14 00:53:17

Opera浏览器宣布集成ChatGPT 一键生成网页内容摘要

Opera浏览器宣布集成ChatGPT 一键生成网页内容摘要2023-02-14 00:32:08

谷歌google计划重返进入中国市场?但结果可能令你失望

谷歌google计划重返进入中国市场?但结果可能令你失望2023-02-13 16:57:15

Zoom紧急裁员1300人 佔员工总数15%

Zoom紧急裁员1300人 佔员工总数15%2023-02-08 14:59:11

最新资讯

YouTube更新违反规定政策,提升惩处透明度和一致性2023-12-31 14:00:52

YouTube更新违反规定政策,提升惩处透明度和一致性2023-12-31 14:00:52 美国法院裁定阿里须为Squishmallows玩具侵权案答辩2023-12-28 19:59:34

美国法院裁定阿里须为Squishmallows玩具侵权案答辩2023-12-28 19:59:34 小米汽车传员工3700人 雷军称小米汽车不可能卖9万92023-12-28 19:41:57

小米汽车传员工3700人 雷军称小米汽车不可能卖9万92023-12-28 19:41:57 吉利飙逾6% 电动车品牌极氪新车款极氪007昨上市 预售价格22.99万元2023-12-28 19:30:28

吉利飙逾6% 电动车品牌极氪新车款极氪007昨上市 预售价格22.99万元2023-12-28 19:30:28 日本丰田汽车厂11月全球产量创新高2023-12-28 19:26:02

日本丰田汽车厂11月全球产量创新高2023-12-28 19:26:02

手机

中国11月手机出货量增34% 5G手机出货量2709.2万部2023-12-28 19:27:57

中国11月手机出货量增34% 5G手机出货量2709.2万部2023-12-28 19:27:57 荣耀发布新一代旗舰荣耀Magic5系列,新款上市价格分期0首付3999元起2023-03-06 16:12:32

荣耀发布新一代旗舰荣耀Magic5系列,新款上市价格分期0首付3999元起2023-03-06 16:12:32 美国商务部指违禁,长江存储被美国拜登制裁名单面临停工裁员2023-02-17 18:41:53

美国商务部指违禁,长江存储被美国拜登制裁名单面临停工裁员2023-02-17 18:41:53 苹果Apple iOS车载系统CarPlay支持哪些更多汽车品牌2023-02-02 17:33:27

苹果Apple iOS车载系统CarPlay支持哪些更多汽车品牌2023-02-02 17:33:27 香港去哪买三星手机回来吗? 买香港便宜售价手机市场地点和网站2023-02-02 11:03:11

香港去哪买三星手机回来吗? 买香港便宜售价手机市场地点和网站2023-02-02 11:03:11

数码

华为5G芯片正式亮相:预示华为将发首款5G手机2023-08-31 13:22:33

华为5G芯片正式亮相:预示华为将发首款5G手机2023-08-31 13:22:33 腾讯传计划放弃虚拟现实VR硬件计划2023-02-17 23:32:30

腾讯传计划放弃虚拟现实VR硬件计划2023-02-17 23:32:30 三星手机份额大跌!三星手机中国市场份额变化国内仅剩3%2023-02-01 17:06:15

三星手机份额大跌!三星手机中国市场份额变化国内仅剩3%2023-02-01 17:06:15 三星手机份额大跌在中国没市场了!国内市场占有率仅剩1%国外比苹果销量高2023-02-01 16:59:53

三星手机份额大跌在中国没市场了!国内市场占有率仅剩1%国外比苹果销量高2023-02-01 16:59:53 vivo发布2022 vivoNEX手机极简易浏览器下载:简洁流畅无广告!2022-12-02 17:29:30

vivo发布2022 vivoNEX手机极简易浏览器下载:简洁流畅无广告!2022-12-02 17:29:30

科技

中兴受美国制裁事件 被罚了20亿美元过程事件始末 中兴被制裁后公司现状2023-11-02 22:12:46

中兴受美国制裁事件 被罚了20亿美元过程事件始末 中兴被制裁后公司现状2023-11-02 22:12:46 B站怎么炸崩了哔哩哔哩服务器今日怎么又炸挂了?技术团队公开早先原因2023-03-06 19:05:55

B站怎么炸崩了哔哩哔哩服务器今日怎么又炸挂了?技术团队公开早先原因2023-03-06 19:05:55 苹果iPhoneXS/XR手机电池容量续航最强?答案揭晓2023-02-19 15:09:54

苹果iPhoneXS/XR手机电池容量续航最强?答案揭晓2023-02-19 15:09:54 华为荣耀两款机型起内讧:荣耀Play官方价格同价同配该如何选?2023-02-17 23:21:27

华为荣耀两款机型起内讧:荣耀Play官方价格同价同配该如何选?2023-02-17 23:21:27 google谷歌原生系统Pixel3 XL/4/5/6 pro手机价格:刘海屏设计顶配版曾卖6900元2023-02-17 18:58:09

google谷歌原生系统Pixel3 XL/4/5/6 pro手机价格:刘海屏设计顶配版曾卖6900元2023-02-17 18:58:09